목차

0. 조합 논리회로를 들어가며..

지난 시간까지 우리는 조합논리회로의 구성요소들을 살펴보았습니다.

- AND,NOT,OR,NAND,NOR,XOR,XNOR 게이트

- Boolean과 드모르간의 법칙

- 위의 게이트로 구성되어있는 논리회로를 간단하게 정리하는 카르노맵과 Q-M방법

지금부터는 배웠던 요소들을 활용하여 조합 논리회로를 설계해보도록 하겠습니다.

1. 가산기<Adder>

먼저 가산기에 대해서 알아보도록 하겠습니다.

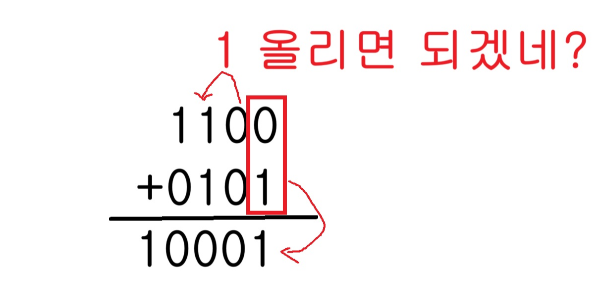

우리는 2진법을 계산할 때 어떻게 계산하나요?

그냥 이런식으로 대충 올림수가 있으니까 올리고, 내릴건 내리고, 머릿속으로 계산을 하거나, 10진법으로 변환해서 계산을 하고 다시 2진법으로 변환하는 방법도 있습니다.

그러나 앞서 봤듯이 컴퓨터는 엄밀하게 말하면 단순하게 게이트에 따른 논리적인 계산, 즉 T냐 F냐밖에 계산을 못합니다.

즉, 2진법이라는 대수적인 개념을 인식하지 못 한다 이말입니다.

그러면, 어떻게 해야 논리적인 계산을 2진법으로 바꿀수가 있을까요?

정답은 가산기에 있습니다.

1-1. 반가산기<Half Adder>

먼저, 반가산기를 보도록 하겠습니다.

반가산기는 한자리 수의 2진수 2개를 입력하여 합과 캐리를 계산하는 조합논리회로입니다.

바로, 예시를 들어서 봅시다.

A와 B는 입력값입니다.

위에서도 언급했다시피 한 자리숫자만을 가리킵니다.

S는 Sum의 약어로 합을 나타내고 C는 Carry의 약어로 자리올림을 의미합니다.

0과 0을 합치면 당연히 합이 0이고 자리 올림도 없죠?

0과 1을 합치면 합이 1이고 올림도 없고요. 1과 0도 마찬가지입니다.

그러나, 1과 1을 합치면 한자리가 올라갑니다. 그러므로 1이 되죠.

여기서 S는 0이 되는데 자리 올림수를 뺀 나머지라 생각하면 됩니다.

이를 진리표로 나타내면 다음과 같습니다.

| A | B | S | C |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

자 여기서 \(S = A \oplus B\)로 나타낼 수 있지 않나요?

입력값에서 1의 갯수가 홀수일때 1이니까 XOR 연산이 나오겠죠?

반면에 \(C=A \cdot B\)로 나타낼 수 있죠?

잘 보면, C는 A와 B가 전부 1일때 1이니까 AND 연산이 나오는게 맞잖아요!

그래서 논리회로를 한번 구성해보면 다음과 같습니다.

이제 슬슬 감이 잡히시나요?

조합논리회로는 이런식으로 구성하면 됩니다!

1-2. 전가산기<Full Adder>

반가산기가 이해가 되면 전가산기는 사실 거저먹기입니다.

앞에서 봤듯이 반가산기는 한자리 숫자만 된다는 점이 문제점입니다.

그것을 보완하기 위해서 전가산기가 나오게 됩니다.

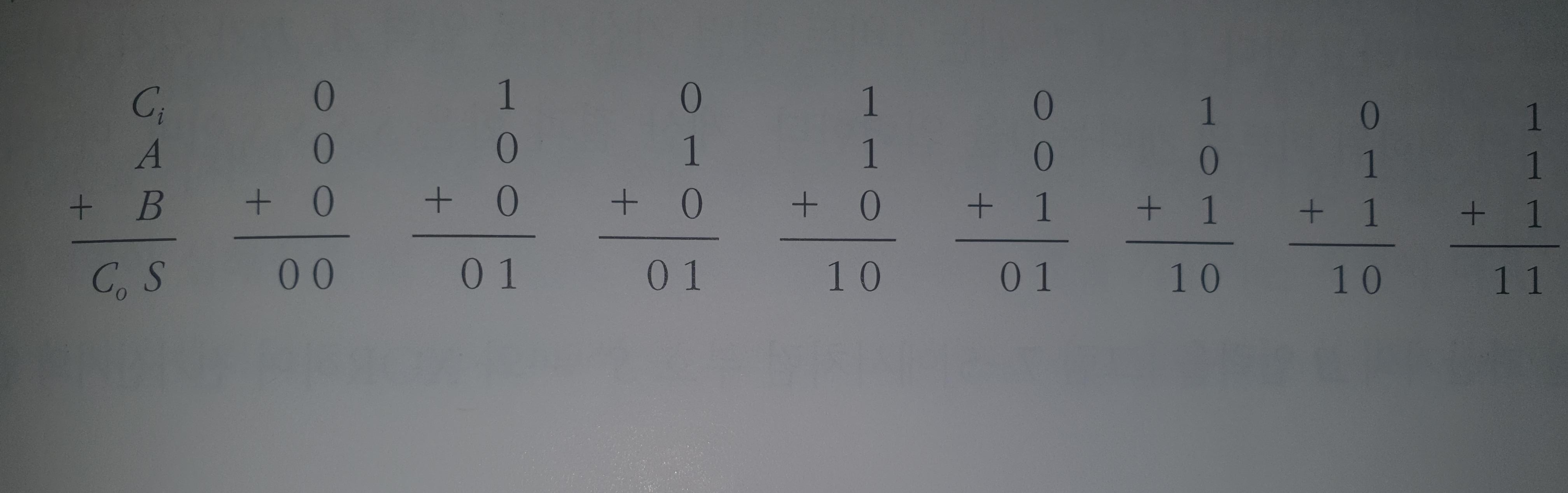

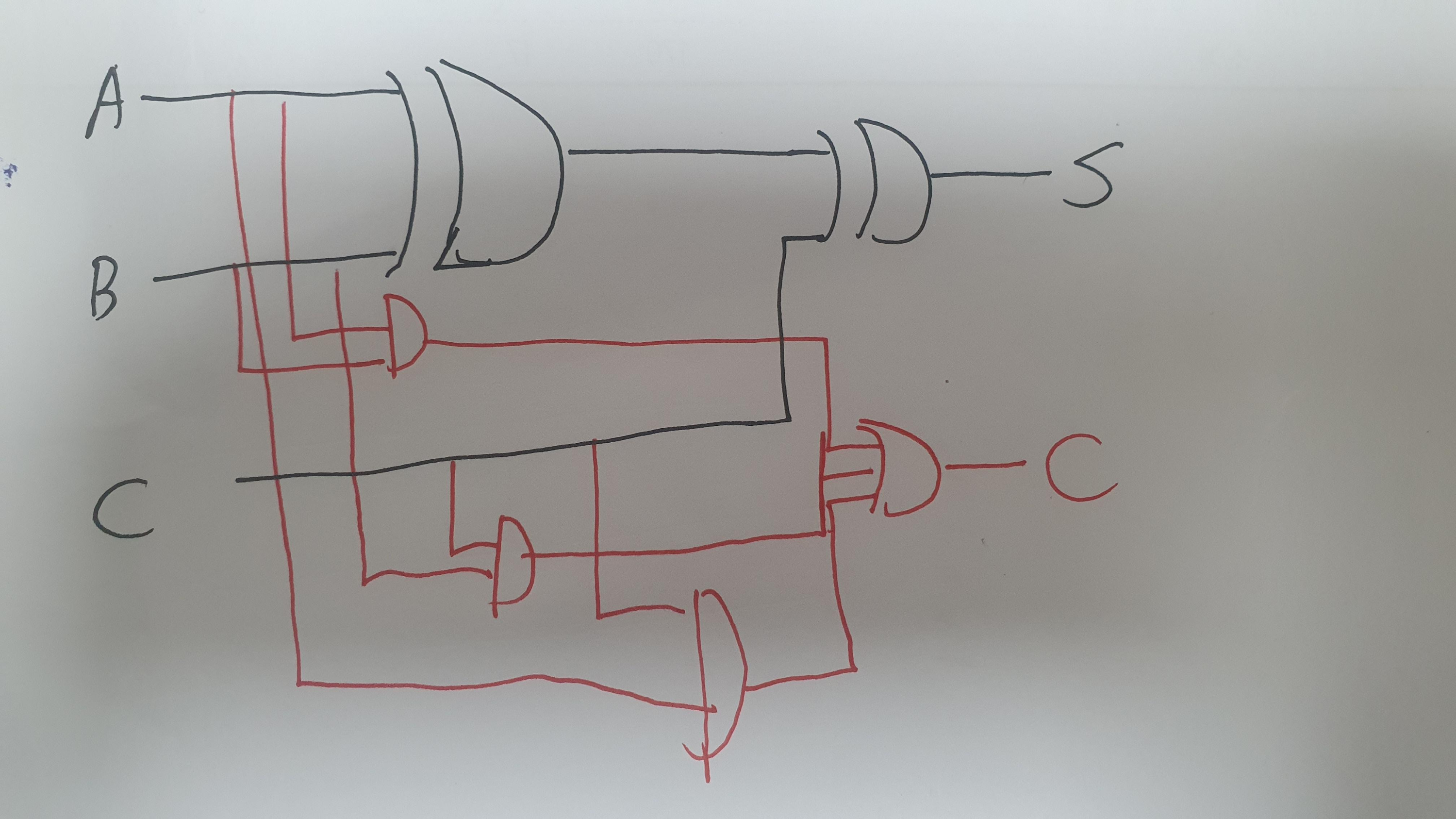

자리올림인 Carry를 이번에는 변수에 추가시켜서 3개의 변수가 전가산기에 사용이 됩니다.

OutPut인 Carry와 Sum도 여전히 존재하구요.

위식을 보면 알겠지만 Input되는 Carry in도 하나의 입력값처럼 취급이 되기에 Ci도 A나 B와 똑같이 취급이 되는게 보일겁니다.

Ci가 1이고 A가 1, B가 0일때 합이 10으로 나오는걸 보면 알 수 있습니다.

그 외에는 반가산기와 별반 다를게 없으니 바로 진리테이블로 봅시다.

위의 테이블을 통해서 한번 Sum의 카르노맵을 그려봅시다.

뭔가 딱히 엮을만한게 없으니까 그냥 불대수로 풀어야 겠네요.

\(S=X\dot{Y}\dot{Z} + \dot{X}\dot{Y}Z + XYZ +\dot{X}Y\dot{Z}\)를 정리해야겠습니다.

\(S=\dot{X}(\dot{Y}Z+Y\dot{Z})+X(\dot{Y}\dot{Z}+YZ)\)

\(S=\dot{X}(Y\oplus Z)+X (\overline{Y \oplus Z}) \)

\(S=\dot{X}A+X\dot{A} \) (단, 여기서 \(A= Y \oplus Z \))

\(S=X \oplus A\)

\(S=X \oplus ( Y \oplus Z )\)로 정리가 됩니다.

이번에는 Carry의 카르노맵을 봅시다.

정리해보면 C = XY+YZ+XZ 네요.

카르노맵의 위력이 바로 이겁니다 ㅎㅎ

이를 총 정리하여 회로를 그리면 다음과 같습니다.

1-3. 병렬 가감산기<Parallel Adder/Subtractor>

위에서 이야기한 전가산기는 한자릿수의 비트연산에 대해서만 해결을 하였습니다.

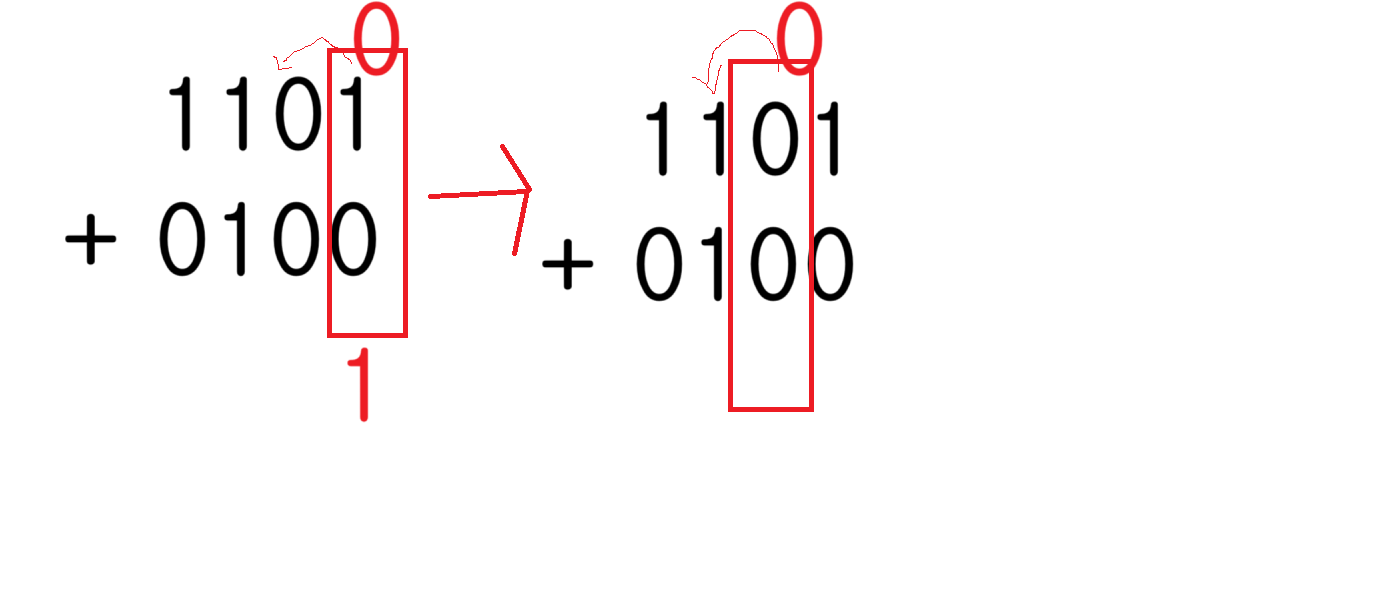

그러면 이제는 1101+110 이렇게 자릿수가 많아지면 어떻게 해야 할까요?

가장 단순하게 접근해보면, 가산기를 그냥 병렬로 쭉 연결하면 됩니다.

한번, 앞에서 배웠던 전가산기의 원리대로 계산을 때려봅시다.

1번째로, 가장 아랫자리인 1과0 에서 먼저 계산이 끝나고, 캐리를 올립니다.

여기서는 캐리가 따로 없으니 0을 올리면 되겠군요.

(지금 한 과정이 바로 회로도에서 S0입니다.)

2번쨰로, 0과 0을 계산합니다.

아까 1번째 단계에서 받은 캐리가 0이군요. 그러니까 일단은 총 0입니다.

(지금 한 과정이 바로 회로도에서 S1입니다.)

3번째로는 1과 1을 계산합니다.

아까 2번째 단계에서 받은 캐리가 0이네요. 하지만 이번에는 캐리가 1이 생겼으니 1을 올립시다.

(지금 한 과정이 바로 회로도에서 S2입니다.)

4번째로는 1과 0을 계산합니다.

이번에는 아까와는 다르게 3번째 단계에서 받은 캐리가 1이네요. 그러므로 1+1+0이니까 캐리가 또 1이 생깁니다. 합은 0으로 취급하고요.

(지금 한 과정이 바로 회로도에서 S3입니다.)

5번째는 캐리밖에 없으니 4번째에서 받은 캐리를 올리면 됩니다.

(지금 한 과정이 바로 회로도에서 S4입니다.)

근데 지금 하는 과정을 보면 뭔가 연산속도에 있어 문제가 있다는 생각이 들지 않나요?

그렇습니다. S0 전가산기에서 계산을 하고 캐리를 받아와서 그걸 S1에게 넘겨주는게 문제입니다.

이를 Ripple-Carry라고 부르는데 이를 해결하기 위해서 고속 가산기라는게 등장합니다.

고속 가산기는 쉽게 생각해서 Carry를 미리 예측하여 이를 미리 계산하여 위로 올리는 방식으로 작동이 됩니다.

여기서는 고속 가산기에 대한 자세한 설명은 생략하겠습니다.

나중에 기회가 되면 다시 다뤄보겠습니다.

2. 비교기<Comparator>

가산기까지 이해하셨다면 비교기는 비교적 쉽습니다.

비교기는 말 그대로 데이터가 같으냐 다르냐를 따지는 논리회로입니다.

어떻게 작동이 되는지는 진리 테이블로 바로 보도록 하겠습니다.

2-1. 1비트 비교기

먼저 입력은 A와 B를 받습니다.

출력은 4가지의 경우의 수로 나뉘는데요.

- A와 B가 같은경우에 참을 나타내는 F1

- A와 B가 다른경우에 참을 나타내는 F2

- A와 B중 A가 큰쪽이면 참을 나타내는 F3

- A와 B중 B가 큰쪽이면 참을 나타내는 F4

F1과 F2는 각각 XNOR, XOR로 표현을 할 수 있습니다.

F3와 F4는 카르노맵을 적용해보면 쉽게 구할 수 있습니다.

(2변수 카르노맵이니 이건 직접 해보시길 바랍니다. ㅎㅎ)

2-2. 2비트 비교기

이제는 2비트 데이터를 비교하는 논리회로를 설계해봅시다.

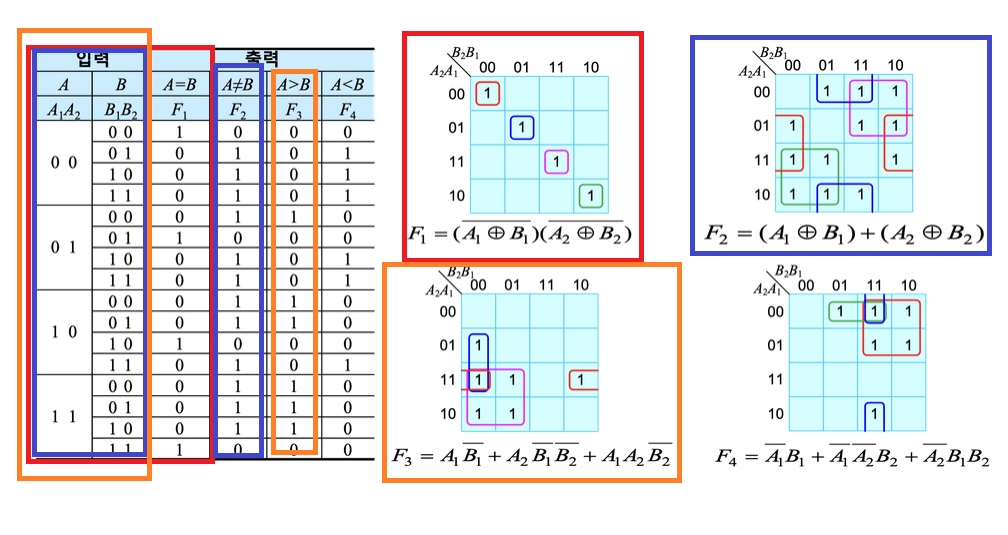

진리 테이블과 카르노맵은 아래 그림을 보면서 이야기 해보겠습니다.

색깔대로 카르노맵을 정리한것이니 아랫단에서 정리를 해보도록 하죠

2-2-1. F1 카르노맵 정리

\(F1 = \dot{A_{2}} \dot{A_{1}} \dot{B_{2}} \dot{B_{1}} + \dot{A_{2}} A_{1} \dot{B_{2}} B_{1}+ A_{2}A_{1} B_{2} B_{1} + A_{2} \dot{A_{1}} B_{2} \dot{B_{1}} \)

\(F1 = \dot{A_{2}} \dot{B_{2}}( \dot{A_{1}} \dot{B_{1}} + A_{1}B_{1}) + A_{2}B_{2}( \dot{A_{1}} \dot{B_{1}} + A_{1}B_{1} )\)

\(F1 = (\dot{A_{2}} \dot{B_{2}}+ A_{2}B_{2} )( \dot{A_{1}} \dot{B_{1}} + A_{1}B_{1} )\)

\(F1 = (\overline{A_{2}\oplus B_{2}})(\overline{A_{1}\oplus B_{1}})\) 로 정리가 됩니다.

2-2-2. F2 카르노맵 정리

\(F2 = (A_{2}\dot{B_{2}}+ \dot{A_{2}}B_{2})+ (A_{1}\dot{B_{1}}+ \dot{A_{1}}B_{1}) \)

\(F2 = ({A_{2}\oplus B_{2}})+({A_{1}\oplus B_{1}})\)

F3와 F4는 그냥 바로 풀어쓰면 되므로 생략하겠습니다.

2-2-3. 최종 회로도 정리

3. 요약정리

- 컴퓨터는 기본적으로 논리연산밖에 할 수 없다. 그래서 논리연산을 대수적으로 변환하기 위해서 가산기라는 논리회로를 사용한다.

- 가산기에는 자리올림수인 Carry와 합인 Sum이 출력으로 존재한다.

- 반가산기는 한 비트단위만 되지만 전가산기는 2비트 연산을 가능하게 한다.

- 비교기는 A와 B의 입력을 받아서 A와 B가 같은 경우, 다른경우, 어느쪽이 큰지에 대한 4가지 경우의 수를 출력으로 한다.

- 카르노맵을 활용하여 식을 간단하게 만들고 이를 논리회로도로 그리면 된다.

'CS 이론 > 디지털 논리회로' 카테고리의 다른 글

| 디지털 논리회로 Part 2 - 0장 <조합 논리회로 VS 순차 논리회로> (0) | 2024.09.29 |

|---|---|

| 디지털 논리회로 10부<Parity Bit와 해밍코드> (0) | 2024.02.14 |

| 디지털 논리회로 9부 <NAND,NOR,XOR 게이트> (0) | 2024.02.14 |

| 디지털 논리회로 8부 <Q-M 방법> (0) | 2024.02.13 |

| 디지털 논리회로 7부<카르노맵 Implicant> (0) | 2024.01.30 |